===========================================================================

Demostratie etaj radioemisie .Linii de cod in C

===========================================================================

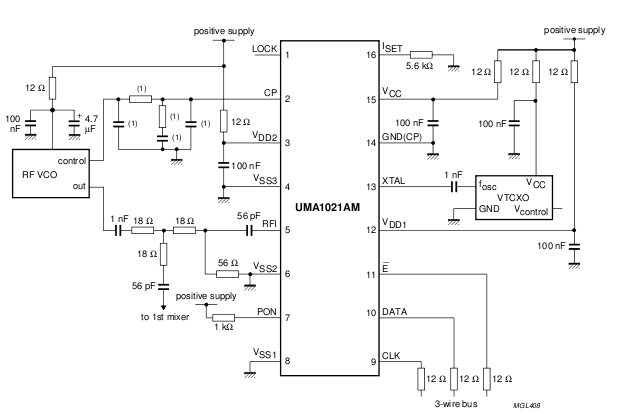

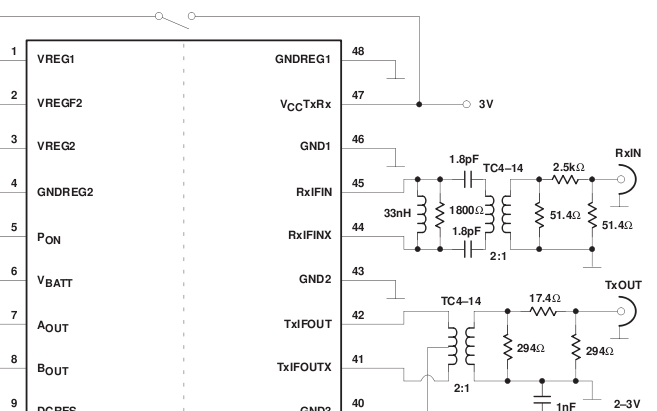

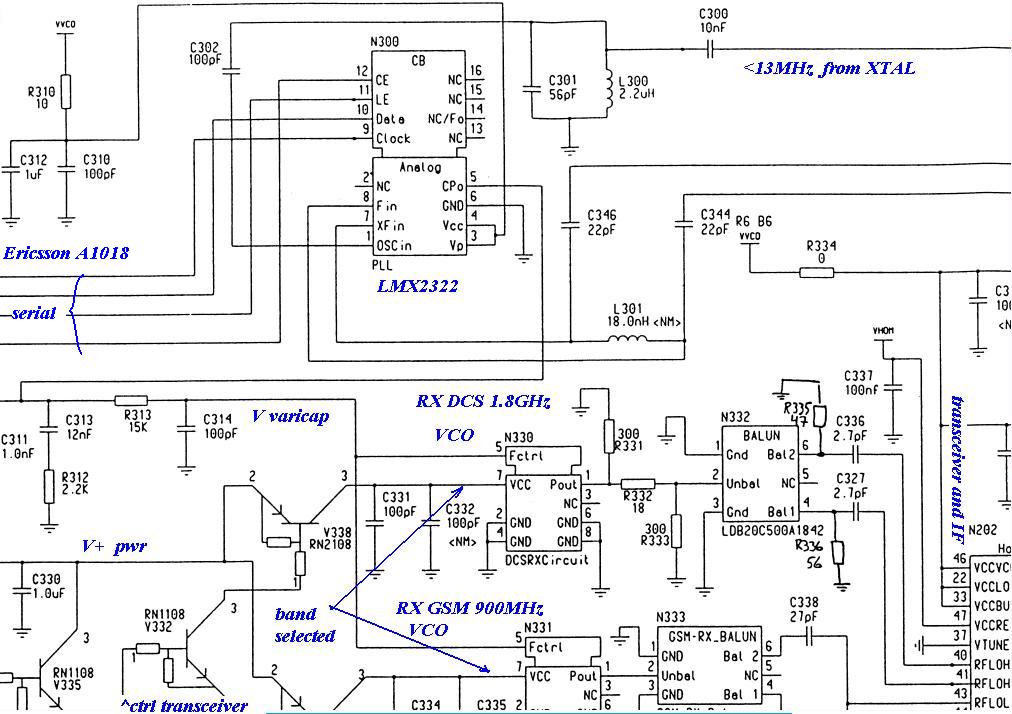

Schema de principiu pentru intregratul PLL.

Tensiunea pe pinii 1 si 2 monitorizata.

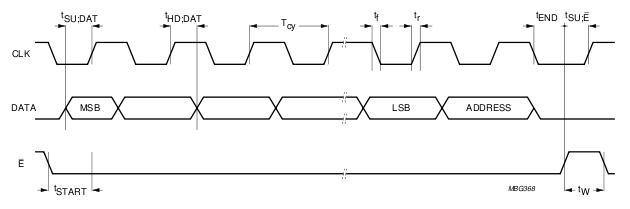

Formele de unda pentru cele 3 fire seriale de control.

Semnalul E(enable negat) trebuie mentinut pozitiv. Activ E este 0-logic.

Frecventa de referinta intre 3 si 35MHz,tipic 13MHz.

Pinul 7-PON trebuie sa fie la potential pozitiv (pentru PLL activ).

Dupa lecturarea cu atentie a dataseheet-ului configuratia va fi astfel(cel mai semnificativ primul):

Demostratie etaj radioemisie .Linii de cod in C

===========================================================================

Schema de principiu pentru intregratul PLL.

Tensiunea pe pinii 1 si 2 monitorizata.

Formele de unda pentru cele 3 fire seriale de control.

Semnalul E(enable negat) trebuie mentinut pozitiv. Activ E este 0-logic.

Frecventa de referinta intre 3 si 35MHz,tipic 13MHz.

Pinul 7-PON trebuie sa fie la potential pozitiv (pentru PLL activ).

Dupa lecturarea cu atentie a dataseheet-ului configuratia va fi astfel(cel mai semnificativ primul):

900MHz frecveta principala, 13MHz referinta.

Divizare 17 biti principal 11 biti referinta, respectiv. 131 071 si 3777 inzecimal

900MHz / 131 071=6.8KHz

13MHz/3777=3.4KHz

Compararea fazei e face la 200KHz.

13MHz/65 (divizor referinta)=200KHz

900MHz/4500(divizor pprincipal)=200KHz

Se va verifica daca primele trei canae 'se pot obtine' astfel:

Canal 0 TX 890 RX 935, 4450 respectiv 4675 divizor principal

Canal 1 TX 890.2 RX 935.2, 4451 respectiv 4676

Canal 2, TX 890.4 RX 935.4, 4452 respectiv 4677

925MHz ''cade" la mijloc inte benzile RX si TX; 925MHz/200KHz=4625

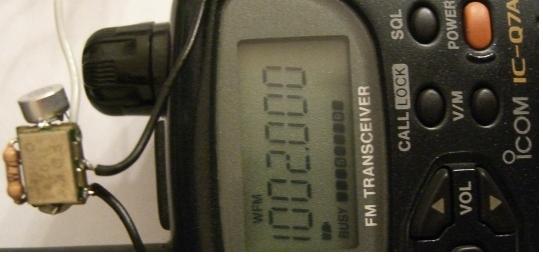

Etajul radio este controlat de catre DSP. Daca la alimetarea cu +5V (la pornire) avem indicatia de semna insemna ca erajul radio fuctioneaza corect.

Totusi traseele DSP -> PLL (comanda) vor fi intrerupte, iar semnalele de control seriale vor veni de la PIC16F.

Au fost facute conexiuni la pinii interfetei seriale ai integratului UMA1021 (PLL-ul). Fiecare din cei trei pini ai interfetei are un condensator SMD la masa, ceea ce face mai usoara lipirea. Acesti condensatori contribuie la asigurarea timpiulor minimi CLK, DAT, Not E.

"Unde duc" aceste fire ale interfetei seriale va fi cautat cu ohmetrul.

Ies in evidenta semnalele de pornire a unitatii RF, pinii 62,63,64,63 (pini ai DSP GSM).

In cadrul unitatii radio apre UMA1019, care este un echivalent petru UMA1021.

Pentru controlul interfetei seriale, aveam in figura semnalele RFCLK pin 52 si RFD0 pin 60.

Alti pini din interfata RF:

PDSYN - oprire sinteza de frecvventa. 1-logic oprit

TXKEY1 - oprire amplificator de putere final

TXKEY2 - contrrol modul putere (trigger)

PDBIAS - oprste alimetarea emisiei

NPDBIAS - Not PDBIAS

PDTX<1,2>, PDRX<1,2> -control transceiverym7rkyi

NPDTX<1,2> - Negat PDTX<1,2>

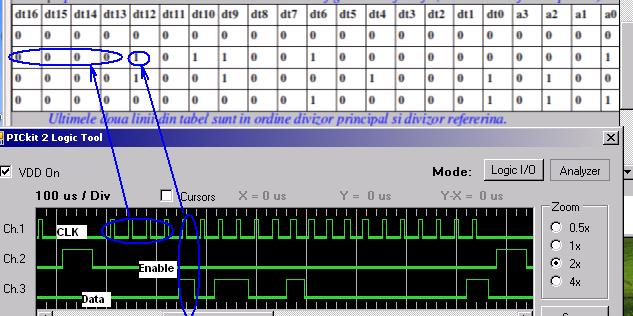

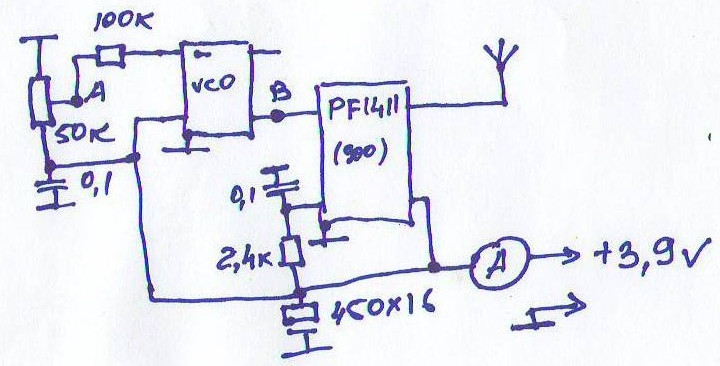

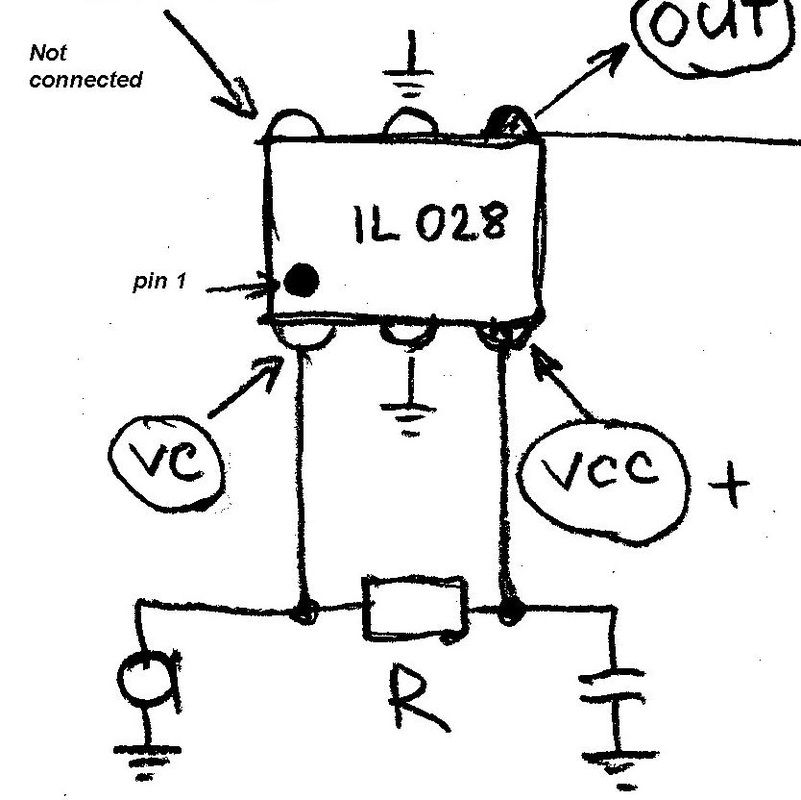

Pe un PCB de test este pus un PIC16F684 si un afisaj 7-seg. Se realiseaza astfel o configuratie mimima pentru test UMA1021:

RA0,RA1 din 16F684 sunt folosite atat pentru programare ca DAT, resectiv CLK, cat si ca intrarea in analizorul logic. Este folosit softul PicKIt2 v.2.61(Tools-> Logic).

Programul scris in MikroC porneste de la un long integer , x, si pe iesirea DAT sunt pusi pe rand biti lui x, incepend cu bitul 20, in ordine descrescatoare.

Analizate cele trei iesiri DAT, CLK si N Enable.

Modul de test este urmatorul: programul are delay initial 2s, ceea ce permite ca dupa bifarea Vdd On, pornirea alimentarii se se apese butonul RUN, astepta secventa de inceput, "cadrea in 0" a liniei N Enable.

DSP-ul nu a fost deconectat, controlul magistralei se face pe baza capabilitatii in curent a pinilor de ieire. DSP-ul poate debita sau "absorbi'' maxim 20mA/pin, in timp ce PIC16F 200mA/pin.

Si alimentarea integratului PLL UMA1021 este controlata. El functioneaza doar in anumite momente dictate de DSP. Astfel, alimetarea integratului si pinul 7 (respectiv 7+8 in varianta de pe placa), adica PON , ambele vor fi coevtat direct la tensiunea de alimetare 5V.

Testele arata ca integratul raspunde controlului soft, dar inca DSP-ul il mai controleaza.

Pe ieirea CP pinul 2 se monteazaun voltmetru in configuratie PLL VCO corecta.

Ramane astfel doar intrarea XTAL, 13MHz frecventa de referinta sa fie oprita de catre DSP.

In continuare se vor identifica cuarturile de pe placa iincercand sa observam si modul lor de control.

Laga DSP (nr.8) avem cuartul de 32.768KHz (ceas, nr.10), care ajunge pe pinii 29 si 30 ai DSP, respectiv CLK32O, CLK32I. Acesta poate folosi la indentificarea pinului 1 al DSP, desi pinul 1este marcat.

Un alt cuart este folsit de integratul SA1638BE, transceiverul de frecventa intermediara:

Are imaginea unei configuratii clasice a unui oscilator cu cuart (condensatorii plus rezistenta in partea dreapta cuartului). Firele din stanga, ambele vor fi puse la alimetare 5V.

Firele din dreapata ajung in pinii 45 si 44 ai lui SA1638, respectiv Rx IF IN si Rx IF INX.

Pe pinii 44 si 45 sunt semnale care intra direct din oscilator. Urmarind PCB-ul, aveam ca schma de principiu este respectata in mare parte.

Voltajul pe CP, voltmetru (conecatat invers).

Cele doua comutatoare sunt pe DAT si CLK care coincid cu pinii de programare. In timpul programarii DAT si CLK spre PLL sunt deconecatate.

Divizare 17 biti principal 11 biti referinta, respectiv. 131 071 si 3777 inzecimal

900MHz / 131 071=6.8KHz

13MHz/3777=3.4KHz

Compararea fazei e face la 200KHz.

13MHz/65 (divizor referinta)=200KHz

900MHz/4500(divizor pprincipal)=200KHz

Se va verifica daca primele trei canae 'se pot obtine' astfel:

Canal 0 TX 890 RX 935, 4450 respectiv 4675 divizor principal

Canal 1 TX 890.2 RX 935.2, 4451 respectiv 4676

Canal 2, TX 890.4 RX 935.4, 4452 respectiv 4677

925MHz ''cade" la mijloc inte benzile RX si TX; 925MHz/200KHz=4625

Etajul radio este controlat de catre DSP. Daca la alimetarea cu +5V (la pornire) avem indicatia de semna insemna ca erajul radio fuctioneaza corect.

Totusi traseele DSP -> PLL (comanda) vor fi intrerupte, iar semnalele de control seriale vor veni de la PIC16F.

Au fost facute conexiuni la pinii interfetei seriale ai integratului UMA1021 (PLL-ul). Fiecare din cei trei pini ai interfetei are un condensator SMD la masa, ceea ce face mai usoara lipirea. Acesti condensatori contribuie la asigurarea timpiulor minimi CLK, DAT, Not E.

"Unde duc" aceste fire ale interfetei seriale va fi cautat cu ohmetrul.

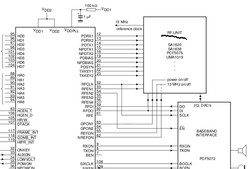

Ies in evidenta semnalele de pornire a unitatii RF, pinii 62,63,64,63 (pini ai DSP GSM).

In cadrul unitatii radio apre UMA1019, care este un echivalent petru UMA1021.

Pentru controlul interfetei seriale, aveam in figura semnalele RFCLK pin 52 si RFD0 pin 60.

Alti pini din interfata RF:

PDSYN - oprire sinteza de frecvventa. 1-logic oprit

TXKEY1 - oprire amplificator de putere final

TXKEY2 - contrrol modul putere (trigger)

PDBIAS - oprste alimetarea emisiei

NPDBIAS - Not PDBIAS

PDTX<1,2>, PDRX<1,2> -control transceiverym7rkyi

NPDTX<1,2> - Negat PDTX<1,2>

Pe un PCB de test este pus un PIC16F684 si un afisaj 7-seg. Se realiseaza astfel o configuratie mimima pentru test UMA1021:

RA0,RA1 din 16F684 sunt folosite atat pentru programare ca DAT, resectiv CLK, cat si ca intrarea in analizorul logic. Este folosit softul PicKIt2 v.2.61(Tools-> Logic).

Programul scris in MikroC porneste de la un long integer , x, si pe iesirea DAT sunt pusi pe rand biti lui x, incepend cu bitul 20, in ordine descrescatoare.

Analizate cele trei iesiri DAT, CLK si N Enable.

Modul de test este urmatorul: programul are delay initial 2s, ceea ce permite ca dupa bifarea Vdd On, pornirea alimentarii se se apese butonul RUN, astepta secventa de inceput, "cadrea in 0" a liniei N Enable.

DSP-ul nu a fost deconectat, controlul magistralei se face pe baza capabilitatii in curent a pinilor de ieire. DSP-ul poate debita sau "absorbi'' maxim 20mA/pin, in timp ce PIC16F 200mA/pin.

Si alimentarea integratului PLL UMA1021 este controlata. El functioneaza doar in anumite momente dictate de DSP. Astfel, alimetarea integratului si pinul 7 (respectiv 7+8 in varianta de pe placa), adica PON , ambele vor fi coevtat direct la tensiunea de alimetare 5V.

Testele arata ca integratul raspunde controlului soft, dar inca DSP-ul il mai controleaza.

Pe ieirea CP pinul 2 se monteazaun voltmetru in configuratie PLL VCO corecta.

Ramane astfel doar intrarea XTAL, 13MHz frecventa de referinta sa fie oprita de catre DSP.

In continuare se vor identifica cuarturile de pe placa iincercand sa observam si modul lor de control.

Laga DSP (nr.8) avem cuartul de 32.768KHz (ceas, nr.10), care ajunge pe pinii 29 si 30 ai DSP, respectiv CLK32O, CLK32I. Acesta poate folosi la indentificarea pinului 1 al DSP, desi pinul 1este marcat.

Un alt cuart este folsit de integratul SA1638BE, transceiverul de frecventa intermediara:

Are imaginea unei configuratii clasice a unui oscilator cu cuart (condensatorii plus rezistenta in partea dreapta cuartului). Firele din stanga, ambele vor fi puse la alimetare 5V.

Firele din dreapata ajung in pinii 45 si 44 ai lui SA1638, respectiv Rx IF IN si Rx IF INX.

Pe pinii 44 si 45 sunt semnale care intra direct din oscilator. Urmarind PCB-ul, aveam ca schma de principiu este respectata in mare parte.

Voltajul pe CP, voltmetru (conecatat invers).

Cele doua comutatoare sunt pe DAT si CLK care coincid cu pinii de programare. In timpul programarii DAT si CLK spre PLL sunt deconecatate.

=========================================

unsigned long x;

char n,a,k;

/////////////////////////////////////////////////////////////////////////

for (k=1;k<5;k++) {

if (k==1) x=0; // cele patru stringuri e trimis contin si adresa

if (k==2) x=0x16401;

if (k==3) x=0XFFFFFFF4;

if (k==4) x=0XFFFFF5;

RA5_bit=0; //date

Delay_uS(15);

for(n=0;n<21;n++) { // 20 de biti penr sir trimis

asm { movf _x+2,w //octet din margine

movwf _a

btfss _a,4

bcf PORTA,5 /// RA5 date ieisre

btfsc _a,4

bsf PORTA,5

nop

nop

nop

nop

nop

nop

nop

nop

bsf PORTA,0 /// clock RA0 in ijlocul datei trimise

nop

nop

nop

nop

nop

nop

nop

nop

bcf PORTA,0 };

x=x<<1; //// shift

};

Delay_uS(10);

RA5_bit=0;

Delay_uS(15);

RA1_bit=1;

Delay_uS(55); };

/// Am neglijat Enable care va fi actv pe perioada transmisiei

==================================================================================

=================================================================================

O realizare de pe vrtp.ru - emisie in frecventa inalta:

http://vrtp.ru/index.php?showtopic=2481

unsigned long x;

char n,a,k;

/////////////////////////////////////////////////////////////////////////

for (k=1;k<5;k++) {

if (k==1) x=0; // cele patru stringuri e trimis contin si adresa

if (k==2) x=0x16401;

if (k==3) x=0XFFFFFFF4;

if (k==4) x=0XFFFFF5;

RA5_bit=0; //date

Delay_uS(15);

for(n=0;n<21;n++) { // 20 de biti penr sir trimis

asm { movf _x+2,w //octet din margine

movwf _a

btfss _a,4

bcf PORTA,5 /// RA5 date ieisre

btfsc _a,4

bsf PORTA,5

nop

nop

nop

nop

nop

nop

nop

nop

bsf PORTA,0 /// clock RA0 in ijlocul datei trimise

nop

nop

nop

nop

nop

nop

nop

nop

bcf PORTA,0 };

x=x<<1; //// shift

};

Delay_uS(10);

RA5_bit=0;

Delay_uS(15);

RA1_bit=1;

Delay_uS(55); };

/// Am neglijat Enable care va fi actv pe perioada transmisiei

==================================================================================

=================================================================================

O realizare de pe vrtp.ru - emisie in frecventa inalta:

http://vrtp.ru/index.php?showtopic=2481

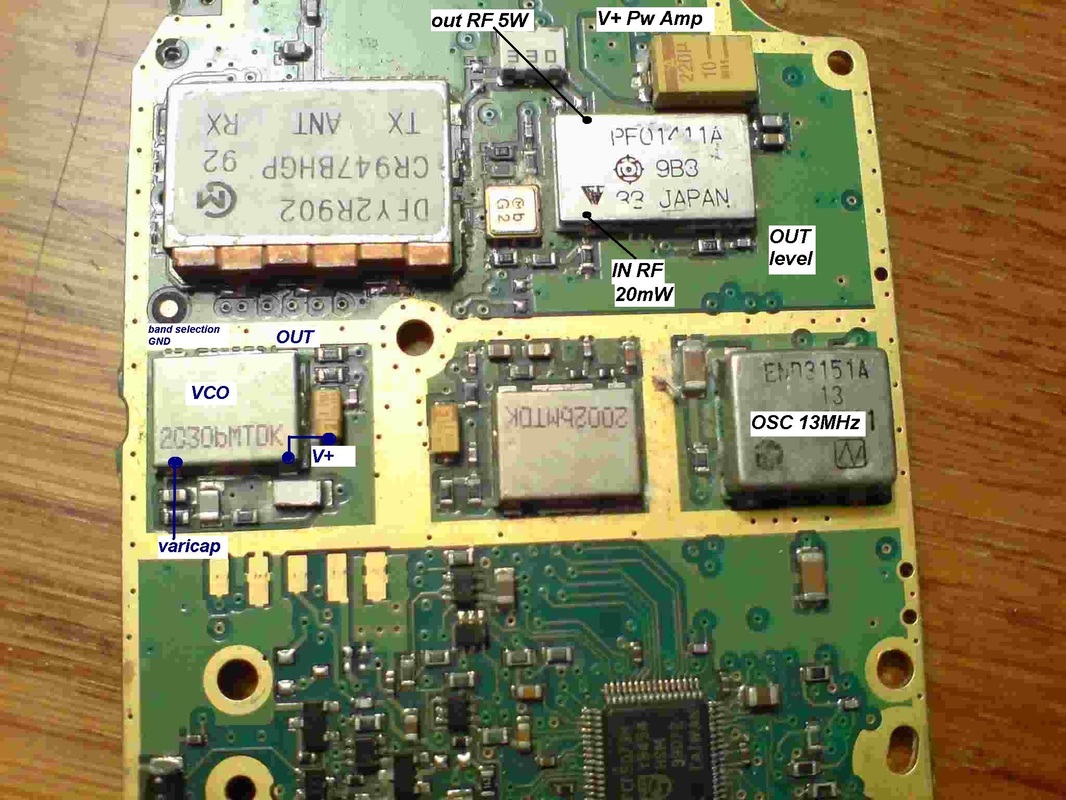

Asezarea componentelor pe placa lui Philips Diga.

Apoi, avem o imagine a unei parti din schema lui Ericsson A1018, mai precis a etajului radio. In mare parte configuratia este aceeasi.

Apoi, avem o imagine a unei parti din schema lui Ericsson A1018, mai precis a etajului radio. In mare parte configuratia este aceeasi.